## Committed to Memory

## SP-HSLV-TS40ULPF High Speed Single Port Compiler

**Low voltage.** Mobile Semiconductor's SP-HSLV-TS40ULPF memory compiler generates single-port SRAM instances using the TSMC 40nm ULP CMOS process. Each low voltage memory instance uses standard  $V_{\rm T}$  to optimize performance with high  $V_{\rm T}$  and source biasing to minimize standby currents. Read and write assist circuits ensure reliable operation with a power supply as low as 0.72V.

**Ultra low power data retention.** Memory instances generated by the SP-HSLV-TS40ULPF go into a deep sleep mode that retains data at minimal power consumption.

**Self biasing.** The SP-HSLV-TS40ULPF's internal self-biasing capabilities provide ease of IP integration.

**Soft error immunity.** Robust, low voltage latches are used throughout designs.

**High yield.** To ensure high manufacturing yield, the SP-HSLV-TS40ULPF utilizes TSMC's high  $V_T$  6T (0.242 $\mu^2$ ) bit cells and is consistent with TSMC's Design for Manufacturing (DFM) guidelines for the 40nm ULP process.

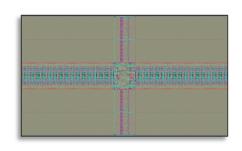

**High usability.** All signal and power pins are available on metal 4 while maintaining routing porosity in metal 4.

| assist circuits                                                            | GDS II Layout                       |

|----------------------------------------------------------------------------|-------------------------------------|

|                                                                            | LVS SPICE Netlist                   |

| ion. Memory e SP-HSLV- ep mode that esumption. e-TS40ULPF's rovide ease of | Liberty File<br>(NLDM and CCS)      |

|                                                                            | Verilog Model                       |

|                                                                            | Verilog Netlist                     |

|                                                                            | Verilog RTL Wrapper                 |

|                                                                            | Verilog Test Bench                  |

|                                                                            | ATPG Verilog                        |

| low voltage<br>gns.<br>ULPF utilizes<br>'s Design for                      | LEF                                 |

|                                                                            | BIST Synthesis<br>Control File      |

|                                                                            | Signal Integrity<br>Analysis Models |

| e maintaining                                                              | PDF and Text<br>Datasheets          |

| '                                                                          |                                     |

**Memory Compiler**

**EDA Views**

& Outputs

| Process Technology    | TSMC 40nm ULP             |

|-----------------------|---------------------------|

| Supply Voltage        | 0.72V to 1.21V            |

| Operating Temperature | -40°C to +125°C           |

| Operating Frequency   | 200MHz to 500MHz          |

| # Metal Layers        | 4                         |

| Power                 | Mesh                      |

| BIST Mux Interface    | Internal                  |

| Operational Modes     | Functional, BIST and Scan |

| Max Instance     | 512Kb                   |

|------------------|-------------------------|

| Min Instance     | 256b                    |

| Word Width       | 4–128                   |

| Word Depth       | 64–8192                 |

| Aspect Ratio     | Column Fold,<br>8 or 16 |

| Bit Write Enable | Optional                |

| User Interface   | GUI &<br>Command Line   |